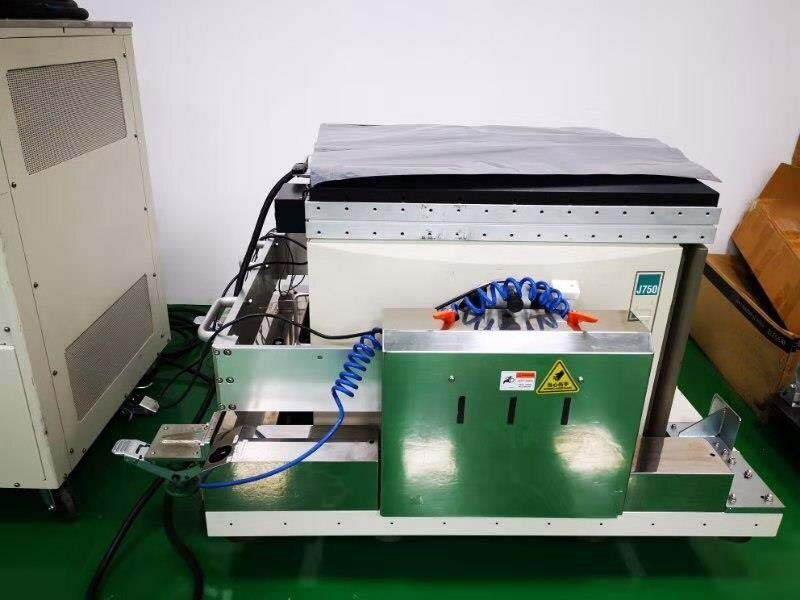

판매용 중고 TERADYNE J750 #9314722

URL이 복사되었습니다!

확대하려면 누르십시오

ID: 9314722

빈티지: 2001

Tester

Test head frame: 512

64 Pin / Channel card

(8) Cards

512 Channels

LVM 16 M

Date rate: 100 MHz

Edge placement accuracy: ± 500 Ps

(2) DPS (8 Channels / board)

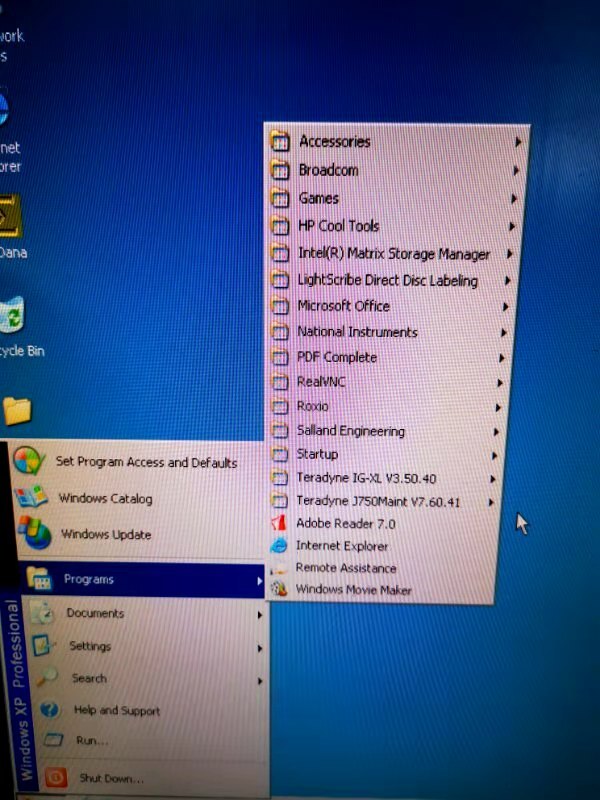

IGXL: 3.40.13

Workstation: Pentium-Xeon

Computer: XW8400 / Z800

Tester and handler communication: DIO Handler

With I/F board PCIT (918-338-20)

YAC Manipulator

2001 vintage.

TERADYNE J750 최종 테스트 장비 (Final Test Equipment) 는 반도체 장치, 디지털 집적 회로, 디지털 신호 프로세서 등 다양한 구성 요소에 대해 정확하고 안정적인 데이터를 제공하는 고속, 고효율 테스트 시스템입니다. 자동차, 소비자, 산업용 등 다양한 전자 제품을 테스트하는 데 이상적입니다. TERADYNE J 750은 견고하고 모듈식 아키텍처를 기반으로 구축되어, 정확하고 반복 가능한 테스트 결과를 제공합니다. 고속, 저전압 프로브, 이중 채널 LVDS 기능을 통해 최대 2,500 개의 테스트 포인트를 제공합니다. 이 장치는 여러 전원 수준, 신호 경로, 비디오 신호 (video signal) 를 지원하므로 다양한 구성 요소에 적합합니다. 다목적 테스트 아키텍처는 효율적인 시스템 구성과 빠른 디버그 (debug) 알고리즘을 지원하여 테스트 프로세스 속도를 높입니다. J750 은 정확한 테스트 기능을 갖추고 있어 타겟 애플리케이션 (Target Application) 에서 구성 요소가 제대로 작동할 수 있다는 확신과 엄격한 제어 기능을 제공합니다. 이는 특히 JEDEC, CE, ISO 등의 표준을 충족해야 하는 자동차, 항공 우주 부품 등 높은 신뢰성 애플리케이션에 매우 중요합니다. J 750 은 논리, 타이밍, 신호 무결성, 전력 소비량 등 구성요소의 모든 요소를 테스트할 수 있습니다. 또한 강력한 개발/디버깅 툴을 통해 테스트 개발/디버깅 프로세스를 간소화할 수 있습니다. 여기에는 통합 테스트 생성기 (Integrated Test Generator) 가 포함되며, 이를 통해 컴포넌트에만 적용되는 강력한 테스트를 생성하는 프로세스가 단순화됩니다. 또한 컴파일러 (Compiler) 와 어셈블러 (Assembler) 가 포함되어 있어 사용자 정의 테스트 알고리즘을 위한 쓰기 프로그램과 낮은 수준의 테스트 프로그램을 생성할 수 있습니다. 또한 TERADYNE J750은 동적 링크 라이브러리 (dynamic link library) 지원을 제공하여 테스트 리소스를 표준화된 라이브러리 구성 요소로 결합 할 수 있습니다. 테라 딘 J 750 (TERADYNE J 750) 은 또한 테스트 결과에 쉽게 액세스하고 관리할 수 있으며, 이를 그래픽 보고서로 볼 수 있습니다. 보고서 형식을 사용하면 데이터를 신속하게 분석하고 결과에 따라 작업을 수행할 수 있습니다. 또한 모든 테스트와 결과를 추적, 검증, 아카이빙할 수 있는 추적 기능을 제공합니다. 전반적으로 J750 Final Test Asset은 다양한 테스트 및 검증 목적에 적합합니다. 정확하고 반복 가능한 테스트, 강력한 개발/디버깅 툴, 신뢰할 수 있는 테스트 결과를 통해 다양한 업계의 구성 요소를 테스트하는 데 이상적인 솔루션이 됩니다.

아직 리뷰가 없습니다